今回は、「オープンコレクタ回路を使用する際の設計留意点」についての説明です。

目次

1.初めに

前回説明したように、トランジスタのコレクタ端子が文字通りオープン・未接続になっている状態のことをオープンコレクタ方式と呼びます。

この接続でトランジスタをスイッチングさせることで、コレクタ出力を切り替えます。

これだけ聞くと設計は簡単そうに感じるのですが、実際は流せる電流量などが決まってくるので、コレクタ端子をオープンにする以外にも色々と考えることはあったりします。

そもそも、飽和領域でトランジスタを使用する場合の動きなんかも説明されていることが少ないですしね。

ということで、今回はオープンコレクタ回路を使用する際の設計留意点について解説していきます。

2.オープンコレクタ方式の設計留意点

オープンコレクタ方式では、以下の点について留意する必要があります。

①最大出力電流は飽和領域での使用を想定した妥当な数値となっているか?

②スイッチングのためのベース電圧が妥当な数値となっているか?

一つずつ解説するというよりも、順番に設計していくと自ずと決まってくるパラメータなので、例を使って①②を決める手順を載せていこうと思います。

一応言っておくと、前任者の方の設計回路から『こんな点に気を付けて設計しているんだな』と個人的に感じたので忘れないようにこうしてまとめているのであって、この設計思想が絶対的に正しいとは思わないでくださいね?

マージンの考え方なんかも企業によって違うでしょうし。

3.オープンコレクタ回路を設計する

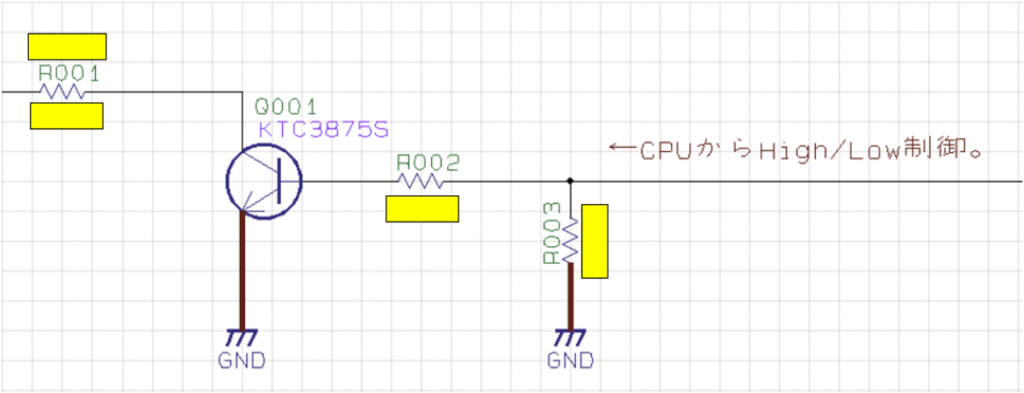

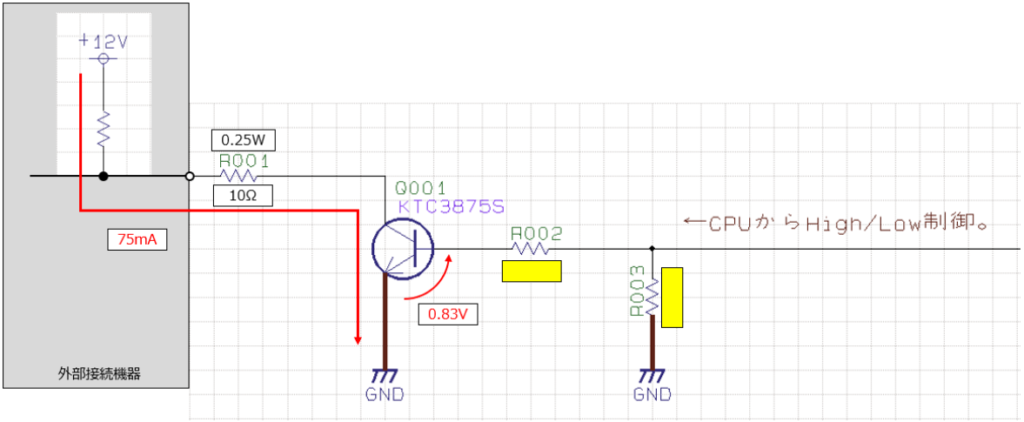

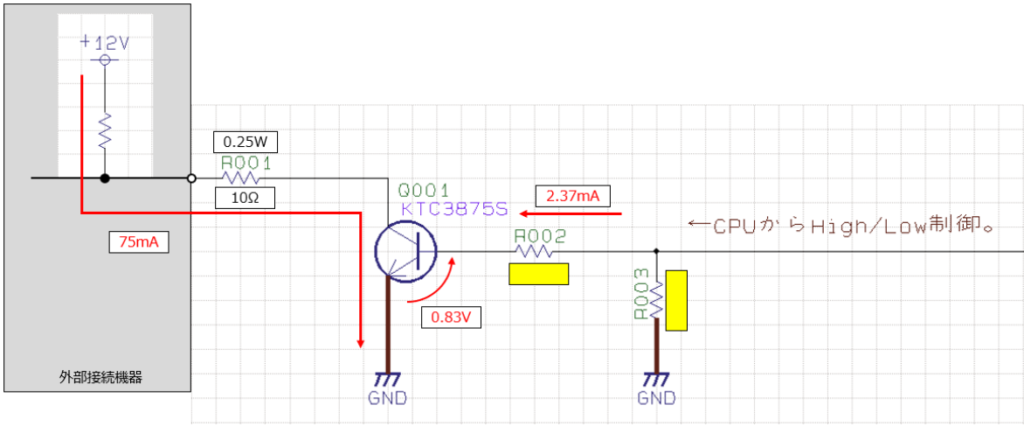

オープンコレクタ方式の基本的な回路構成は、図1のようになります。

ベース端子にCPUのGPIOを繋ぎ、CPUからHigh信号またはLow信号を送り込むことでトランジスタQ001をスイッチング動作させようという魂胆の回路です。

このオープンコレクタ回路に条件付けをし、抵抗定数を決定していきます。

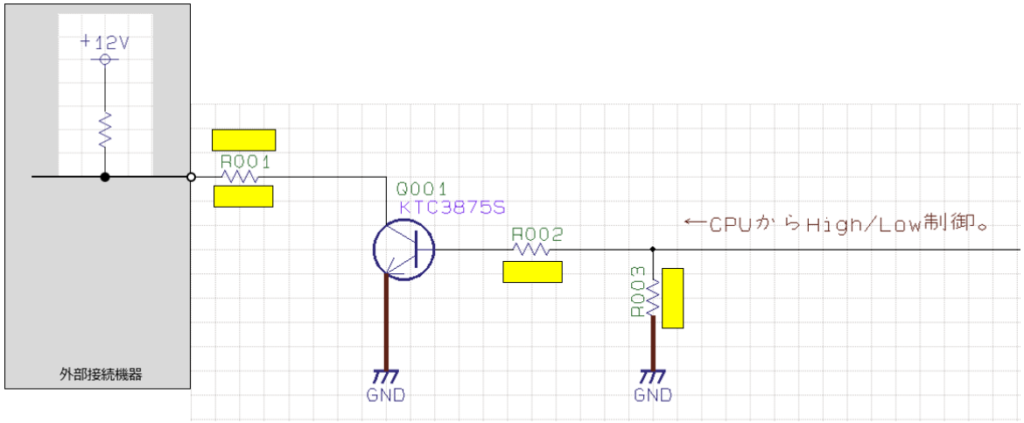

①接続機器の条件付けをする

まず、このオープンコレクタ回路の仕様として、コレクタ端子に印加できる最大電圧は12V、最大電流は75mAとしたとします。

なので、コレクタ端子と外部接続機器の関係は以下のようになります。

この外部接続のプルアップ12VからトランジスタQ001にかけて、最大で75mAまで流せるようにしたいわけです。

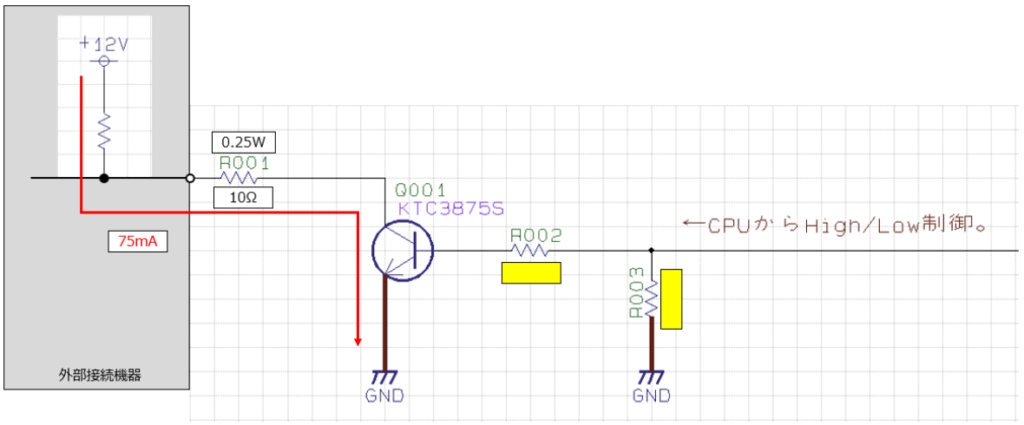

そこで、コレクタ抵抗を10Ωと決め打ちしました。

すると、コレクタ抵抗10Ωには最大で75mAが流れるようになる為、電力=抵抗×電流2の関係から、10Ω×(75mA)2≒56mWの電力が最大で消費されることがわかります。

マージンは2倍以上取ることが多いので、ここでは定格0.25W品の抵抗を使用する必要があります。

割と定格電力が高いので、チップ抵抗ではなく炭素被膜抵抗器・金属皮膜抵抗器辺りを使用することになります。

ちなみに、マージン2倍以上というのは抵抗の定格に限った話ではなく、コンデンサの定格電圧等の他のパラメータにおいても最低限満たすような設計をしていることが多いです。

②オープンコレクタで使用するためのトランジスタの動作を考える

コレクタ電流ICは最大75mAとしたので、このコレクタ電流に対してトランジスタをどのように動作させるのかを考えていく必要があります。

結論だけ先に述べると、ベース-エミッタ間電圧VBEやコレクタ-エミッタ間電圧VCEが飽和(一定値より増加することが無くなること)する領域にて使用することになります。

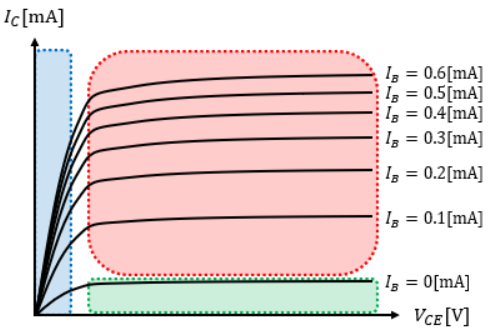

過去の記事で説明した内容が多少被ってくるのですが、トランジスタにてベース電流IBを一定に保った時のIC-VCE特性グラフは以下のようになっています。

これは、ベース電流IBを一定に保った時のIC-VCE特性の関係を表したグラフです。

この特性グラフは、以下の3つの領域に分けることができます。

ベース電流IBが一定なら、コレクタ-エミッタ間電圧VCEによらずにコレクタ電流ICが一定となる領域。

言い換えると、ベース電流IBでコレクタ電流ICが決まる領域です。

ベース電流IBを大きくしてもコレクタ電流ICが増加しない領域。

コレクタ-エミッタ間電圧VCEが小さくても、コレクタ電流ICが流れる領域とも言われる。

ベース電流IBが0[A]でもコレクタ電流ICが0[A]にならず、漏れ電流がわずかに流れる領域。

漏れ電流が大きくてもメリットは無いので、特性の良いトランジスタほど遮断領域が狭くなります。

オープンコレクタ回路の場合はスイッチング動作をさせたいので、飽和領域(スイッチONの状態)と遮断領域(スイッチOFFの状態)を使用します。

飽和領域なら低いコレクタ-エミッタ間電圧VCEでもコレクタ電流ICを流すことが可能なので、コレクタ-エミッタ間での損失を最小限に抑えてスイッチング動作が可能なのです。

だから、ベース-エミッタ間電圧VBEやコレクタ-エミッタ間電圧VCEが飽和する状態でトランジスタを動作させたいのです。

③トランジスタが使用に適しているか確認する

そもそもこのトランジスタを使用して大丈夫かという点も確かめていきます。

今回の回路ではKECのKTC3875Sというトランジスタを使用しようとしているので、これが適しているかを確認しましょう。

この部品のデータシートは、普通にネットで調べれば閲覧出来ます。

データシート上の絶対最大定格を閲覧すると、コレクタ電流IC=150mA、ベース電流IB=30mA、コレクタ電力損失PC=150mWなどの情報が載っています。

これ以降に色んな箇所の電圧・電流を求めていきますが、都度この値を超えないことを絶対条件として考えましょう。

※絶対最大定格は、一瞬たりとも超えてはならないラインのことです。

④コレクタ電流からベース-エミッタ間飽和電圧を読み取る

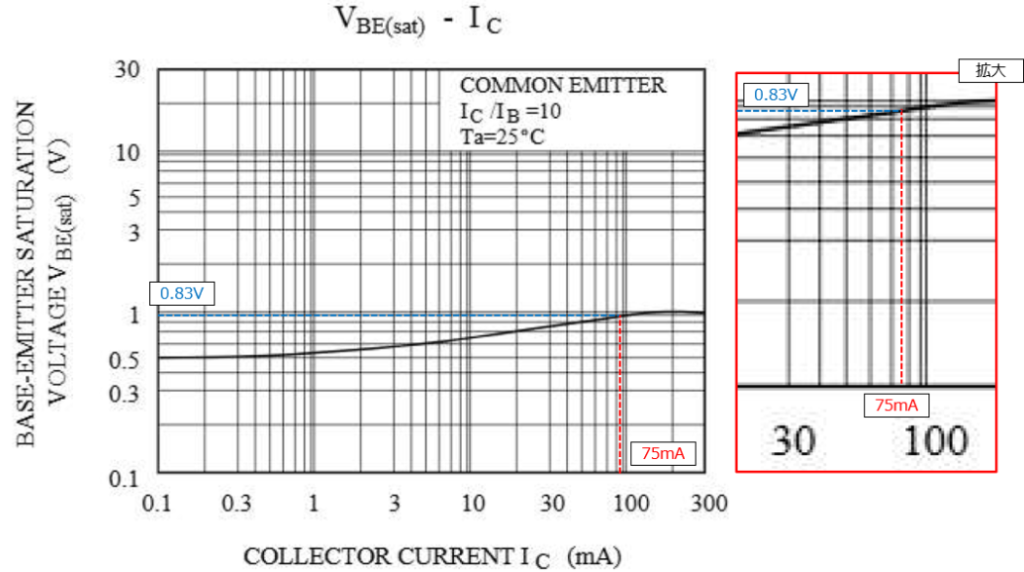

トランジスタのデータシートには様々な特性グラフが載っていますが、その中にコレクタ電流ICとベース-エミッタ間飽和電圧VBE(sat)の特性グラフも存在します。

使用するトランジスタのデータシートによっては載っていない可能性はありますが、少なくとも今回使用しているKECのトランジスタ_KTC3875Sのデータシートには普通に載っていました。

コレクタ端子には最大で75mAまで電流が流れますので、この特性グラフにコレクタ電流IC=75mAの線を引きます。

こうすることで、ベース-エミッタ間飽和電圧VBE(sat)は大体0.83Vだと読み取れます。

この特性グラフは両対数グラフですが、対数グラフの見方がわからない方は以下の記事も参考にしてください。

⑤ベース-エミッタ間飽和電圧からベース電流を読み取る

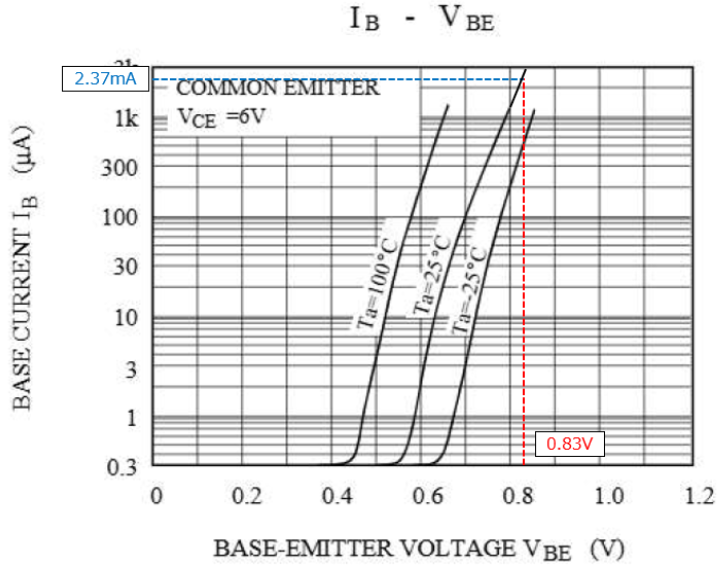

次はベース電流IBとベース-エミッタ間飽和電圧VBE(sat)の特性グラフから、ベース電流IBを読み取ります。

厳密にはベース電流IBとベース-エミッタ間電圧VBEの特性グラフですけどね。

スイッチング動作をさせるためにベース-エミッタ間電圧VBEが飽和している時のベース電流IBを知りたいので、これで良いのです。

今度は片対数グラフになっているので、注意してください。

ベース電流IBは大体2.37mA程度になることがわかりました。

元のグラフの長さが足りないので自分で仮想線を延ばしたり、対数グラフなので細かい値までは読めなかったりしますので、“大体”です。

まあ、コンマ数ミリのズレでダメになるような設計してる方が問題なので、そこまで気にしなくても大丈夫です。

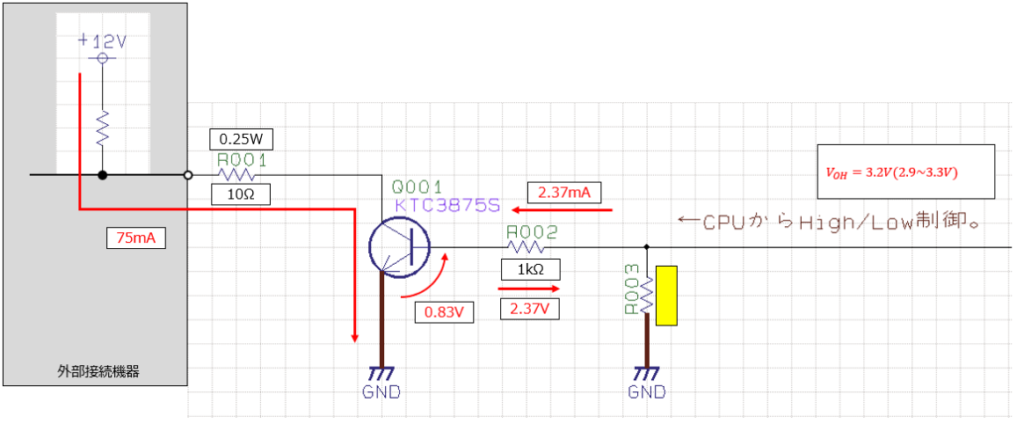

⑥ベース抵抗の定数を選択する

トランジスタQ001を飽和領域で使用するためにはベース電流IBが2.37mA必要だとわかったので、次はベース抵抗R002の定数を決定します。

ベース電流IBが2.37mAということは、ベース抵抗R002には2.37mAが流れることになります。

つまり、ベース抵抗R002の定数次第で、R002の電圧降下が変化します。

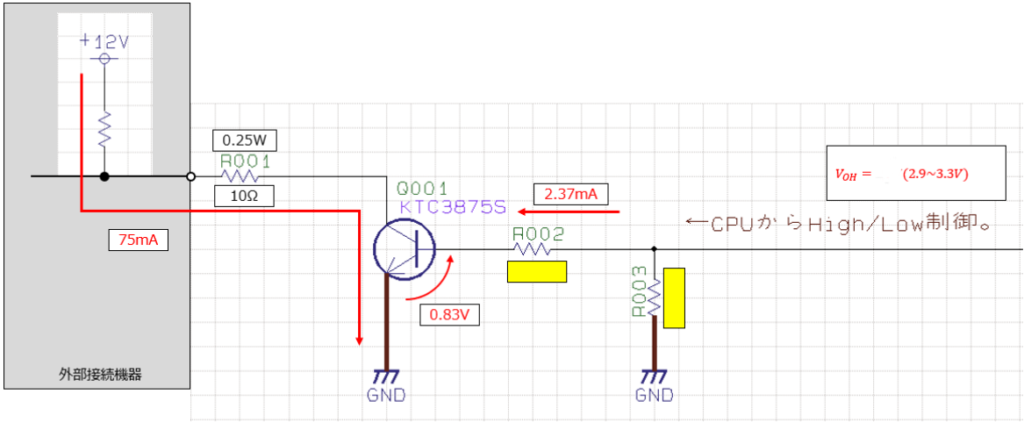

ここで重要になってくるパラメータは、CPUのVOHです。

VOHとは、CPUのGPIO端子が出力端子になっている際のHigh信号の電圧の大きさのことです。

VOLならLow信号になります。

VOHは最低値(Min)が規定されているはずなので、別途規定されているであろうVO(出力電圧の範囲)と合わせて、どんな範囲で電圧を出力できるのかを読み取れます。

ここでは、GPIOの出力電圧の条件が0~VO~VDD(CPUの動作電圧)、VOHはMin VDD-0.4、VDD=3.3Vだったとします。

この場合、VOHの範囲はVDD-0.4~VDD(2.9~3.3V)になります。

これらの条件を図に書き込むと、以下のようになります。

ここで、CPU GPIO端子~トランジスタQ001のベース端子~トランジスタQ001のエミッタ端子~GNDの経路に注目してください。

ベース-エミッタ間電圧VBE(sat)とR002の電圧降下分を足し合わせると、CPU GPIO端子の供給する電圧になっていることがわかるでしょうか?

つまり、0.83V+(R002の端末電圧)が2.9~3.3Vの範囲内に収まっていれば良いのです。

なので、ここではR002を1kΩに設定してみましょう。

こうすると、CPU GPIOからのHigh時の供給電圧は3.2Vとなります。

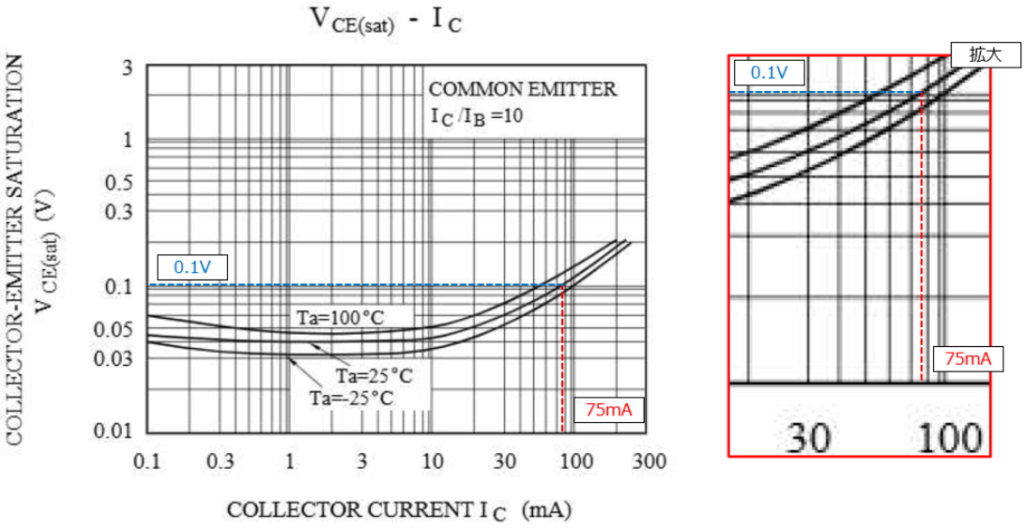

⑦コレクタ電流からコレクタ-エミッタ間電圧を読み取る

絶対最大定格の条件の一つに、コレクタ電力損失PC=150mWというものがありました。

これは、コレクタ-エミッタ間で許容する電力損失のことです。

なので、今回のスイッチング用途におけるコレクタ-エミッタ間飽和電圧VCE(sat)を求める必要があります。

求め方は簡単で、コレクタ電流ICとコレクタ-エミッタ間飽和電圧VCE(sat)の特性グラフを見るだけです。

この特性グラフも、ほぼほぼデータシートで見かけないことは無いはずです。

これでVCE(sat)は約0.1Vだとわかりましたので、PC=VCE(sat)×IC=0.1V×75mA=7.5mWとなります。

コレクタ電力損失PCの絶対最大定格が150mWなのに対して、スイッチング動作では7.5mWしか消費しないということですので、コレクタ電力損失の観点では使用に問題無いことがわかります。

⑧定格電流出力が実際に可能なのか確認する

最後に、オープンコレクタ回路の仕様として最初に設定したコレクタ電流の最大値である75mAを、実際にこの回路で生成出来るのかを確認します。

何故そんな確認が必要なのかと言うと、通常、飽和状態にてトランジスタを使用する場合、電流増幅率hFEが低下するためです。

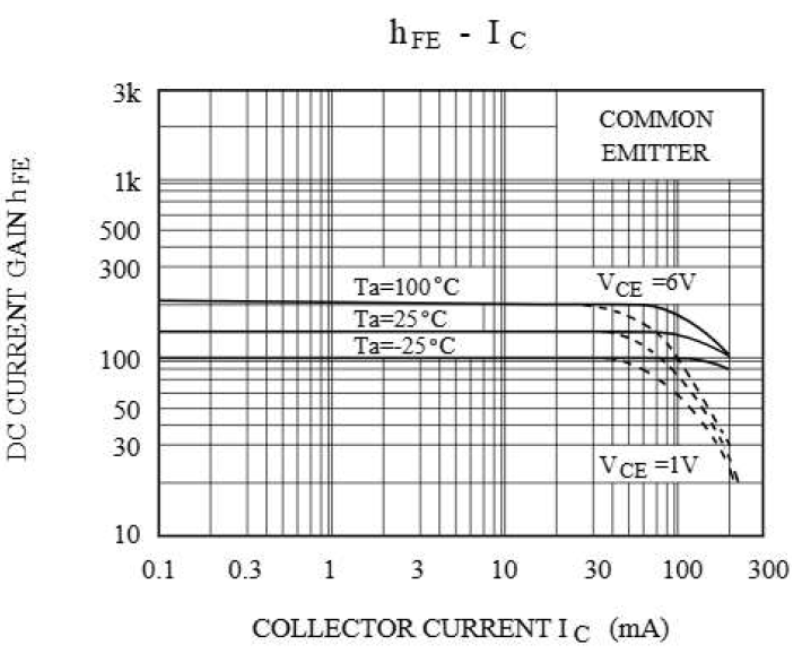

このトランジスタの電流増幅率hFEは70~700になっているので、飽和状態では最小値である70よりも更に小さくなると考える必要があります。

どの程度小さく見積もるのかは会社にもよるかもしれませんが、大体半分程度にしているところが多かったです。

コレクタ電流IC=電流増幅率hFE×ベース電流IBの関係より、コレクタ電流ICの最大値は、(70÷2)×2.37mA≒83mAになります。

設定したコレクタ電流の最大値である75mAを上回っているので、この回路なら75mAは流しても問題無いことがわかります。

ちなみに、電流増幅率hFEとコレクタ電流ICの特性グラフも存在します。

コレクタ電流ICが大きくなるほど、電流増幅率hFEが小さくなっていますね。

VCEが0.1Vの場合のグラフは無いのでどの程度電流増幅率が下がるかは想像しかできませんが、割とギリギリな設計になっていそうです。

まあ、この回路は過去モデルで同じ回路を使用しているという実績があるので、少なくとも問題は無いんですけどね。

⑨おまけ

R003の定数をスルーしていましたが、この抵抗は信号を安定させるためのプルダウン抵抗です。

トランジスタQ001のベース端子に少し電圧がかかるだけでスイッチング動作をしてしまうので、CPUからHigh信号が来ていない時は常にトランジスタがOFF状態になるよう、プルダウンをしています。

そもそもプルダウンって何だと思った方や、定数の決め方がイマイチわからないという方は、以下の記事も参考にしていただくと良いかもしれません。

ちなみに、この回路では4.7kΩのプルダウン抵抗にしていました。

以上、「オープンコレクタ回路を使用する際の設計留意点」についての説明でした。