今回は、「CMOS論理回路」についての説明です。

1.CMOS論理回路とは?

CMOS論理回路とは、p型MOSFETとn型MOSFETの2種類のFETを組み合わせて構成した論理回路のことです。

相補型(Complementary)MOS論理回路のことで、シーモス論理回路と読みます。

市場に出回っている論理演算素子の中身は大体このCMOS論理回路で構成されているのです。

論理回路における基本的な演算回路は以下のような種類がありました。

- AND回路

- OR回路

- NOT回路

- NAND回路

- NOR回路

- XOR回路

この内、NOT回路・NAND回路・NOR回路をCMOS論理回路で表していきます。

ちなみに、CMOSについては別途まとめてありますので、以下の記事も参考にしてみてください。

2.MOSFETの復習

MOSFETの基本だけさらっと補足しておきます。

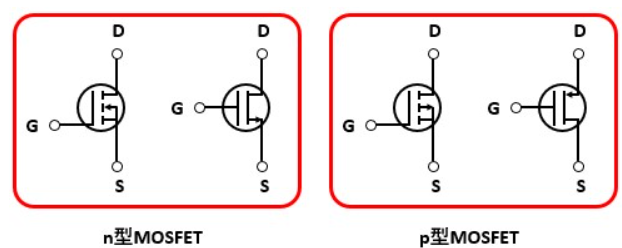

MOSFETの図記号は以下のようになっています。

MOSFETって微妙に色んなパターンで描かれていることがあるんですよね。

FETはゲートに電圧を印加した際の電界によってキャリアの動きを制御します。

n型MOSFETは、ゲートに電圧を印加した時にドレイン-ソース間に電流が流れるようになります。

p型MOSFETは、ゲートに電圧を印加していない時にドレイン-ソース間に電流が流れるようになります。

3.CMOS論理回路(NOT回路)

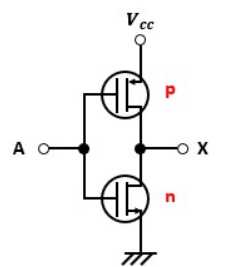

NOT回路をCMOS論理回路で表すと以下のようになります。

本当にNOT回路になっているのか確認してみましょう。

電圧が印加されている時を“1”、電圧を印加していない時(GND接続)を“0”と考えます。

端子Aに電圧を印加した時は、n型MOSFETがON・p型MOSFETがOFFになるので、端子XはGNDに繋がります。

端子Aに電圧を印加していない時は、n型MOSFETがOFF・p型MOSFETがONになるので、端子XはVccに繋がります。

つまり、端子Aが“0”の時は端子Xは“1”、端子Aが“1”の時は端子Xは“0”という関係が成り立っています。

よって、図2はNOT回路だと言えます。

4.CMOS論理回路(NAND回路)

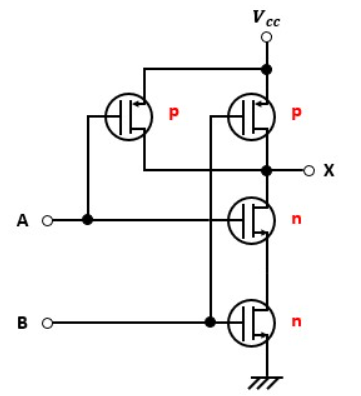

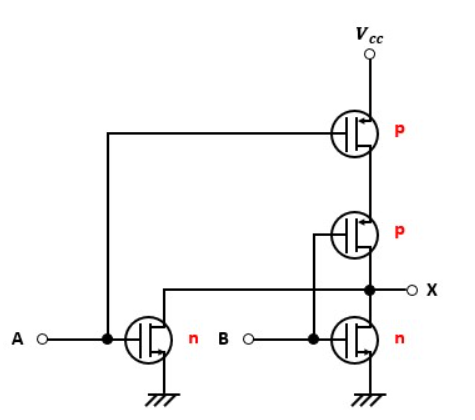

NAND回路をCMOS論理回路で表すと以下のようになります。

見た目が一気にややこしくなりましたが、実は構造は単純です。

というのも、よくよく見るとNOT回路を2つ直列接続しているだけなんですよね。

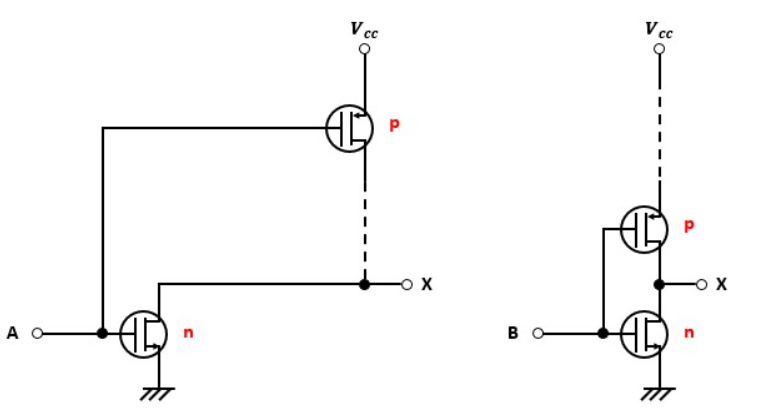

端子Aに関係する回路、端子Bに関係する回路に分けて見ると以下のようになります。

それぞれNOT回路になっているでしょう?

つまり、端子A及び端子Bのどちらかが“0”の時は端子XにVCCが供給されていることになります。

逆に、端子XがGNDに繋がるのは、端子A及び端子Bの両方が“1”になっている時だけになります。

この関係ってどこかで見覚えがないですか?

そう、NAND回路に当たるんですよ。

この2つの回路を同時に満たしてる回路がNAND回路なので、出力を一纏めにして端子Xに集結させた結果、図3のような回路になっているわけです。

5.CMOS論理回路(NOR回路)

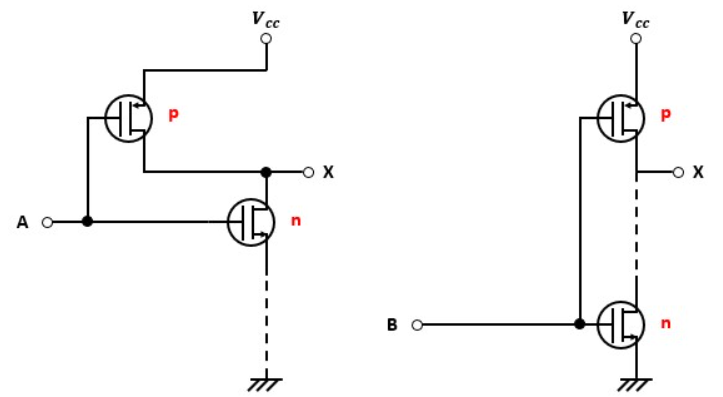

NOR回路をCMOS論理回路で表すと以下のようになります。

NAND回路の説明で察しているのではないかと思いますが、NOR回路はNOT回路を並列接続しているだけです。

今度は、端子A及び端子Bのどちらかが“1”の時は端子XがGNDに繋がり、端子A及び端子Bの両方が“0”の時のみ端子XにVCCが供給されます。

この関係がNOR回路になっているんですね。

以上、「CMOS論理回路」についての説明でした。