今回は、「FETの特性グラフと関連する記号と用語」についての説明です。

目次

1.初めに

過去の記事のFETの動作原理の解説にて、ゲート-ソース間電圧・ドレイン-ソース間電圧の電圧の印加の仕方によって、ドレイン-ソース間電流が流れたり流れなくなったりすることを説明しました。

今回は、その関係が具体的にどのような特性グラフとして表現されているのか、またその特性グラフを表現するに当たって登場する記号・用語の意味についてまとめていきます。

FETに限った話では無いのですが、データシート上には用語の名称だけ書かれていて何を指しているのか書かれていないことはよくあるので、最初は中々理解しづらいんですよね。

2.FETの特性グラフの理解に必要な用語

FETの特性を表す際に、高確率で登場する用語についてまずは説明します。

よく見かけるのは、以下の5つになります。

- VGS

- VDS

- ID

- IDSS

- VP

VGS

ゲート-ソース間電圧のこと。

ベクトル表現と同様、右側のアルファベットが基準となるので、基準はソース端子になる。

VDS

ドレイン-ソース間電圧のこと。

ベクトル表現と同様、右側のアルファベットが基準となるので、基準はソース端子になる。

ID

ドレインーソース間電流のこと。

IDSになっている場合もあるが、何故かIDになっていることがある。

わかりづらいので統一してくれませんかねぇ…?

極性は、ドレイン端子に流れ込む方向が正方向となる。

つまり、ドレインからソース方向に電流が流れる場合は正電流と表現されます。

IDSS

ゲート-ソース間電圧が0[V]の時のドレイン電流のこと。

ドレイン遮断電流と呼ばれている。

他にもID(OFF)など別の記号で表示されている場合もあるが、総じて「遮断しそう」な名称にはなっているはず。

VP

ドレイン電流が流れなくなる時のゲート電圧(厳密にはゲート-ソース間電圧)のこと。

ピンチオフ電圧と呼ばれている。

VGS(OFF)やVGS(TH)などの記号で表示されている場合もある。

ちなみに、定電流ダイオードにて、順方向領域に電圧が変動しても電流値が変化しなくなった時の電流のことをピンチオフ電流と呼びます。

(というか、IDSSが実はここで言うピンチオフ電流に値する。)

なので、“ピンチオフ”と付いていたら、何かしらの値が一定になるパラメータを表していると覚えておくと良いです。

3.FETの特性グラフ

これからJFETの特性グラフとMOSFETの特性グラフについて見ていきます。

主要な特性グラフは、ID-VGS特性とID-VDS特性です。

極性などにちょくちょく差が出てきますが、大まかな形状は一致しているので、あまり身構えないで気軽に見てみましょう。

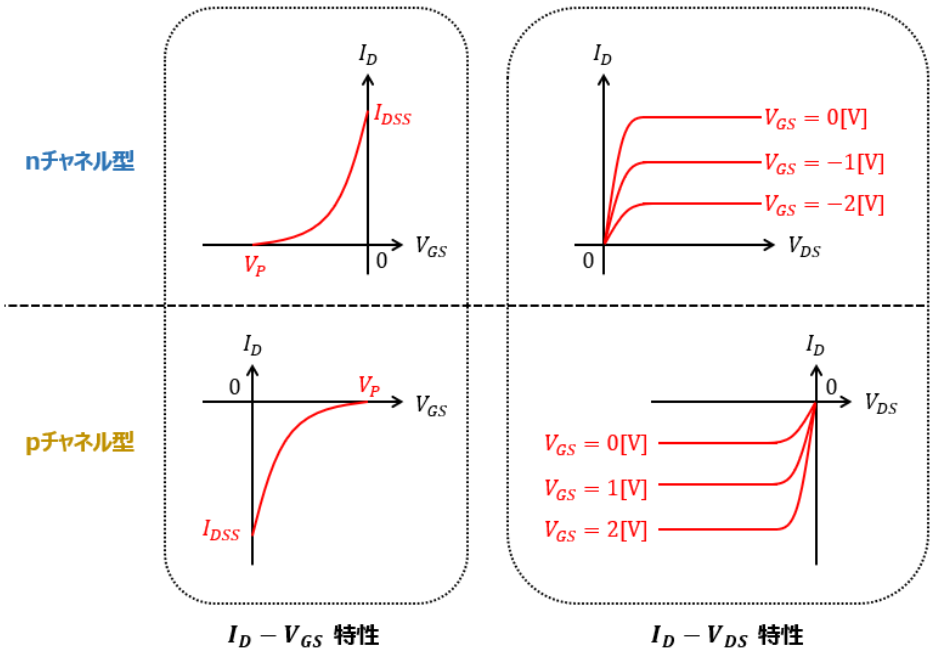

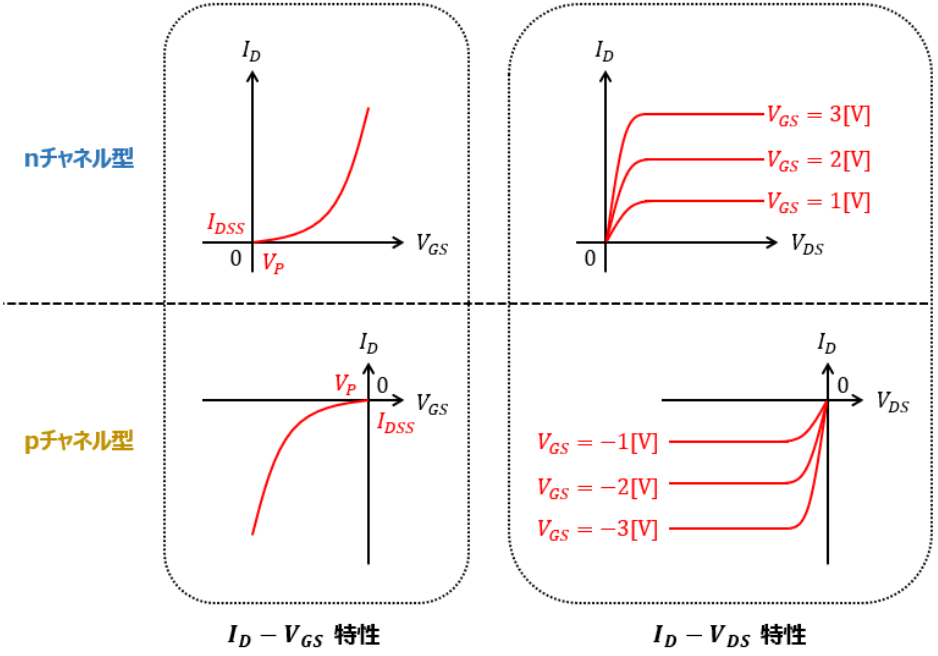

JFETの特性グラフ

JFETの特性グラフをまとめると、以下のようになっています。

グラフだけ見てもよくわからないと思いますので、動作原理の復習も兼ねて順番に見ていきましょう。

まずは、nチャネル型のID-VGS特性から見ていきます。

こちらは見たままなんですけどね。

まず、ドレイン遮断電流IDSSはゲート-ソース間電圧VGSが0[V]の時のドレイン電流IDのことなので、縦軸と交わる点にIDSSがあります。

この時のIDSSは正極性になっていますね。

ということは、ドレイン端子に流れ込む方向に電流が流れていることになります。

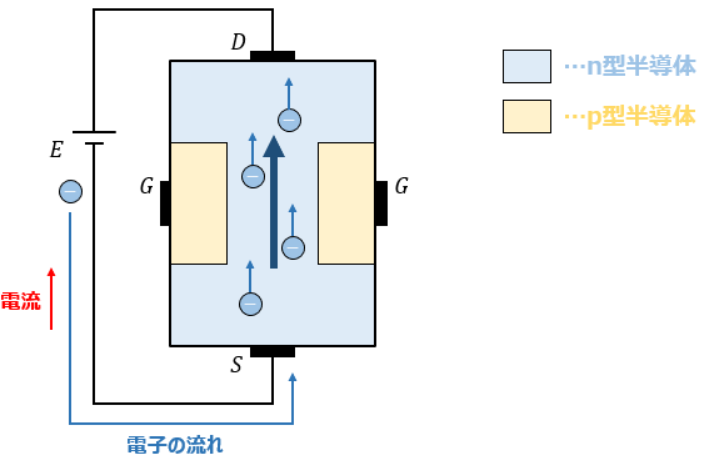

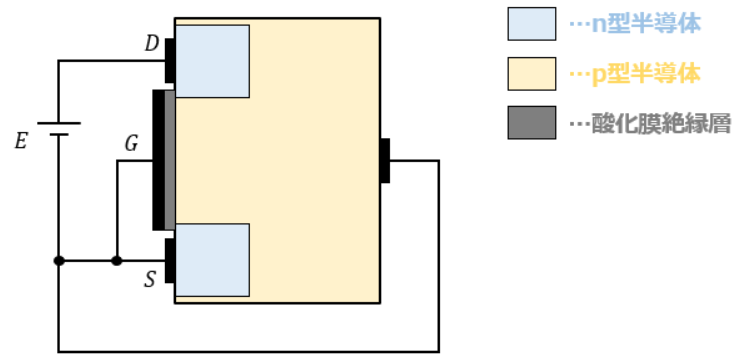

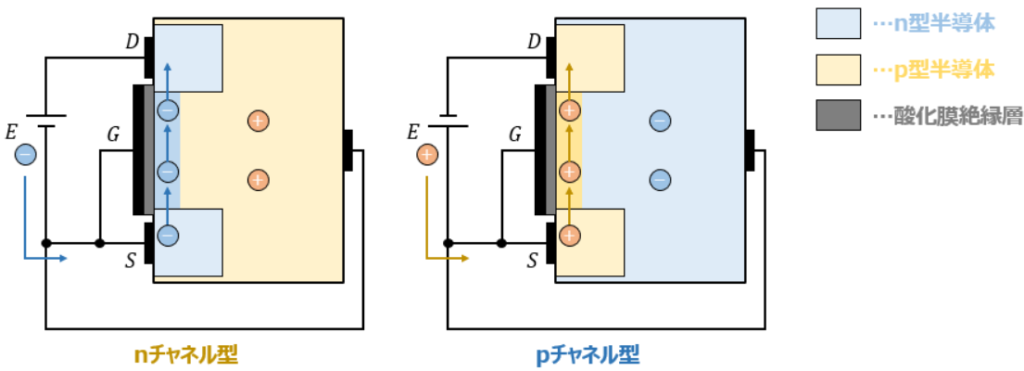

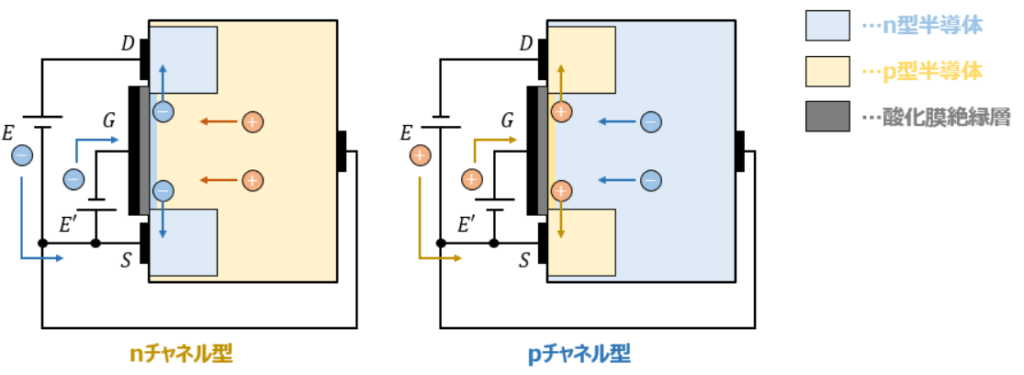

ゲート-ソース間電圧VGSが0[V]の時の動作は以下のようになっていました。

図2を見ると、ドレイン端子に電流が流れ込んでいるでしょう?

この特性を図示しただけなんです。

ピンチオフ電圧VPはドレイン電流IDが流れなくなった時のゲート-ソース間電圧VGSのことなので、横軸と交わる点にVPが存在します。

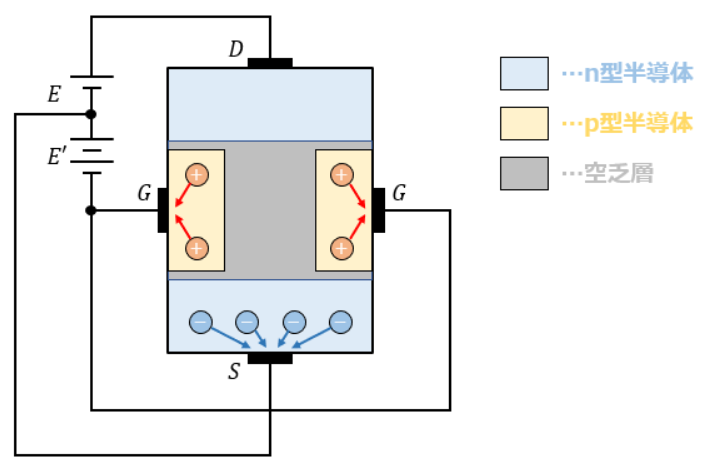

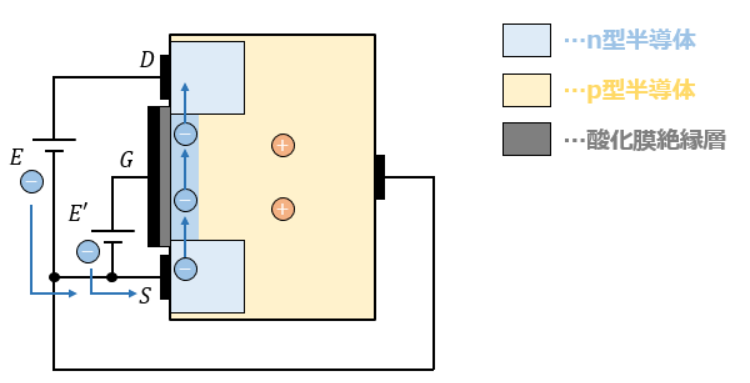

ドレイン電流が流れなくなった時の動作は以下のようになっていました。

この図におけるゲート-ソース間電圧VGSは、起電力E’のことを指しています。

向きを確認すると、ゲートにかかる電圧は負極性になっていますよね?

だからグラフ上のピンチオフ電圧VPも負極性になっているのです。

序盤に述べましたが、ゲート-ソース間電圧VGSの場合、基準はソース端子になるので、ゲートにかかる電圧が正極性ならVGSも正極性になります。

ちょっとややこしいので注意しましょう。

次は、nチャネル型のID-VDS特性を見ていきましょう。

このグラフは、単純にゲート-ソース間電圧VGSが何Vの時にドレイン-ソース間電圧VDSとドレインIDがどんな割合で発生するかを表しているだけです。

JFETは、ゲート-ソース間電圧VGSを特定の方向に印加すると空乏層が大きくなって、ドレイン電流IDが流れなくなります。

その為、VGS=0[V]の時が一番ドレイン電流IDが流れやすいんですよ。

ゲート-ソース間電圧VGSが負極性になるとドレイン電流IDが流れにくくなっていくというのも、ゲート-ソース間電圧VGSを与えることで空乏層が大きくなったが故の変化だというわけです。

動作原理と照らし合わせると、別に何も難しいことは言っていないでしょう?

ただ単品でこの特性グラフだけが出てくるから混乱しやすいだけなんです。

pチャネル型に関しても極性が変わるだけなので説明は割愛します。

試しに動作原理の記事と読み比べながら関係を確認してみると、記憶に定着しやすいですよ?

エンハンスメント型MOSFETの特性グラフ

エンハンスメント型MOSFETの特性グラフをまとめると、以下のようになっています。

nチャネル型のID-VGS特性から見ていきます。

ゲート-ソース間電圧VGSが0[V]の時は、MOSFETに反転層ができていない状態です。

なので、この状態ではドレイン遮断電流IDSSもピンチオフ電圧VPも0になっています。

ここにゲート-ソース間電圧VGSの極性が正になるように電圧を印加していくと、反転層ができてドレイン電流IDが流れるようになります。

この時のドレイン電流IDの向きは、ドレイン端子からソース端子方向なので、極性は正になります。

この関係を図示したら、ID-VGS特性のグラフのようになるでしょう?

次は、nチャネル型のID-VDS特性を見ていきましょう。

先程も述べたように、エンハンスメント型MOSFETのゲート-ソース間電圧VGSが0[V]の場合は、ドレイン電流IDは全く流れません。

反転層を形成する正電圧をゲート端子に印加することでドレイン電流が正極性で流れるようになり、ゲート端子に印加する電圧を大きくしていくとその分反転層が大きくなって電流も流れやすくなります。

その関係を表しただけです。

だからJFETの時と違ってゲート-ソース間電圧VGSが0[V]の時のグラフが描かれていないわけです。

電圧を印加していないと電流は流れない、電圧を印加すると電流が流れるというシンプルな動作をするので、特性グラフと実際の動作の関係をイメージするならエンハンスメント型MOSFETについて考えるのが一番わかりやすいのではないかと思います。

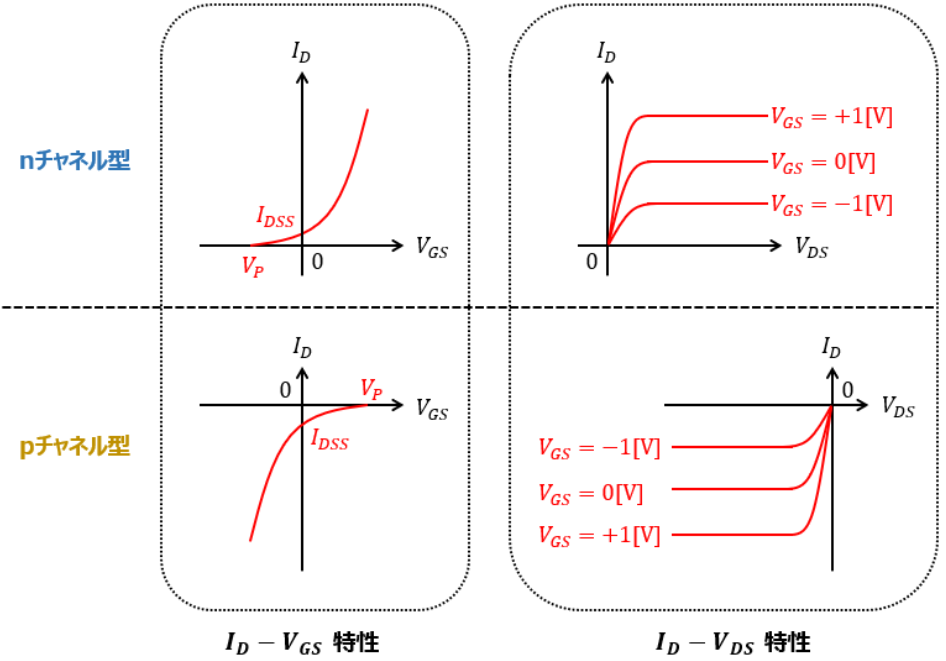

デプレッション型MOSFETの特性グラフ

デプレッション型MOSFETの特性グラフをまとめると、以下のようになっています。

nチャネル型のID-VGS特性から見ていきます。

デプレッション型MOSFETは、ゲート-ソース間電圧VGSを印加していなくても最初から反転層ができています。

なので、ゲート-ソース間電圧VGSが0[V]の時のドレイン電流IDは、中途半端に正方向の電流になっています。

ここから、ゲート-ソース間電圧VGSを正方向に印加すると反転層がより広がってドレイン電流IDが流れやすくなります。

反対に、ゲート-ソース間電圧VGSを負方向に印加すると反転層が狭まっていき、最終的にドレイン電流IDが流れなくなります。

なので、ピンチオフ電圧VPはゲート-ソース間電圧VGSが負方向の位置にあるのです。

次は、nチャネル型のID-VDS特性を見ていきましょう。

先程も述べたように、デプレッション型MOSFETには、ゲート-ソース間電圧VGSが0[V]だったとしてもドレイン電流IDが流れます。

そして、ゲート-ソース間電圧VGSを正方向に大きくするほど反転層が大きくなってドレイン電流IDが流れやすくなり、VGSを負方向に大きくするほど反転層が狭くなってIDが流れにくくなります。

この関係を表しただけです。

動作原理をよくよく思い返しながら特性グラフを眺めてみると、ごく当たり前の関係しか描かれていないんですね。

以上、「FETの特性グラフと関連する記号と用語」についての説明でした。