今回は「クロック信号(CLK/MCLK/WCLK/BCLK)」についての説明です。

1.初めに

クロック信号って聞いたことありますか?

回路図を見たことがある人は、何かしらのICの接続信号にCLKやCKという表記を見かけたことがあるかと思います。

アレはクロック信号のことです。

MCLK/WCLK/BCLKなんかもクロック信号の一種です。

[clock(時計)]機能なので大体どんなことを意味しているのかわかるかもしれませんが、微妙に種類が多くて違いも含めるとイメージしづらいんですよね。

ということで、今回はクロック信号とは何なのか、どんな種類があるのかを簡単にまとめてみました。

2.クロック信号とは?

クロック信号とは、動作タイミングを合わせるために一定の周期を繰り返す信号のことです。

その名の通り[clock(時計)]の役割を持つ信号ということです。

信号名としてはCLKやCKと省略されていることが多いです。

電子機器には様々なICが搭載されていて、あるICと別のICが通信していることは何ら珍しいことではありません。

これらのICの伝送路は一本で構成していることが多く、この場合は片側のICがデータを送信している時はもう片側のICがデータを受信する構えを取っている必要があります。

キャッチボールで投げ手と受け手がいるようなものです。

キャッチボールをする時に、お互いにボールを用意して同時に投げたりしないでしょう?

そこで役に立つのがクロック信号です。

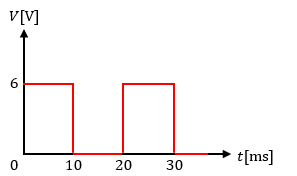

クロック信号は一定間隔でHighレベルとLowレベルが切り替わります。

所謂方形波というヤツです。

なので、片側のICはHighレベルの時に送信/Lowレベルの時に受信、もう片側のICはLowレベルの時に送信/Highレベルの時に受信という具合に設定することで、一定間隔でデータの送受信ができるようになります。

要するに、時計を見ながら○秒経過するごとに送信受信を切り替えているようなものです。

このクロック信号を利用して何かを同期させている場合、その信号はSYNC(synchronizationの略称)と表示されていることがあります。

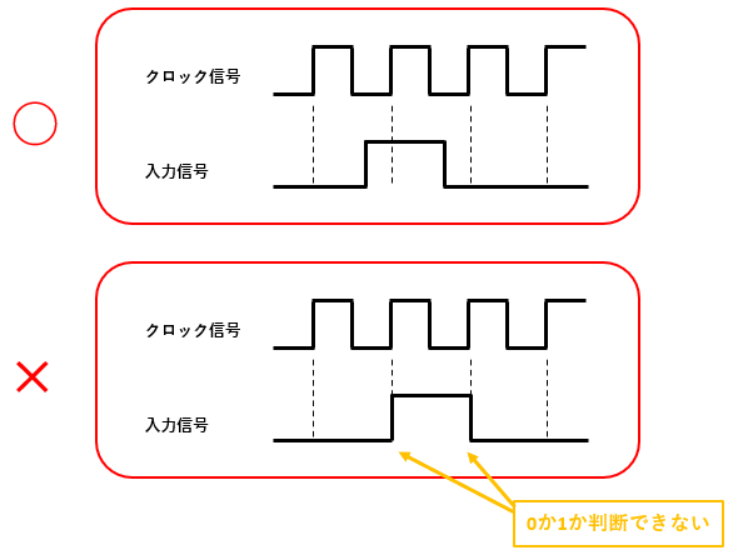

基本的にはクロック信号が立ち上がるタイミングでデータを読み取るようになっているので、クロック信号の立ち上がりのタイミングで入力信号が変化しないように時間的余裕を設けているのが一般的です。

データを読み取っている最中にデータが0から1に変化したら困るでしょう?

3.クロック信号の種類(CLK/MCLK/WCLK/BCLK)

クロック信号の種類としては、マスタークロック(MCLK)・ワードクロック(WCLK)・ベースクロック(BCLK)などが存在します。

何に使用するクロック信号なのかわかりやすいように、名称が変わっているだけですけどね。

その名の通り、マスター機(親機)とスレーブ機(子機)の動作タイミングを合わせるためのクロック信号です。

マスター機→スレーブ機にまとめて送りつけます。

名称からは想像しづらいのですが、音声信号をデジタル伝送する際のクロック信号を指しています。

また、BCLKに関してはビットクロックを指していることもあるようなのですが、ビットクロックについては調べてもあまり情報が出て来なかったです。

どう言ったものなのかハッキリしたら追記しようと思いますので、参考程度に留めておいてください。

以上、「クロック信号(CLK/MCLK/WCLK/BCLK)」についての説明でした。