今回は「クロック信号の立ち上がり/立ち下がりが歪んだ場合の影響と除去しなければならない理由」についての説明です。

1.初めに

クロック信号というと、綺麗な方形波を思い描く人が多いのではないでしょうか?

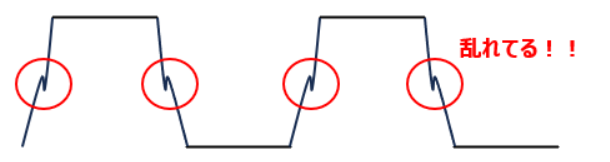

実際は拡大するとちょっと台形っぽい形になります。

ですが、実際のクロック信号をいざオシロスコープで観察してみると、立ち上がり/立ち下がりの際になんか波形が歪んでいることがあります。

クロック信号に限った話ではないですが、このような歪みが発生していると誤動作に結びつくことがあります。

今回は、クロック信号の立ち上がり/立ち下がりが歪んでいると何故誤動作し兼ねないのかを説明していこうと思います。

2.クロック信号の用途について

まず、そもそもクロック信号はどのような用途で使用されているかの復習です。

クロック信号にはMCLK(マスタークロック)やWCLK(ワードクロック)などの種類がありますが、どのクロック信号にしろ動作タイミングを合わせるために一定の周期を繰り返す信号のことをクロック信号と呼びます。

例えば、周期100msのクロック信号があったとすると、山と谷(1周期)を10回繰り返すと合計で1秒経過することになります。

ということは、クロック信号の立ち上がりもしくは立ち下がりの数を数えていれば、10回数えると1秒経過することがわかるのです。

このように、クロック信号の立ち上がり/立ち下がりの回数で経過時間が把握できるので、あるICの起動までの準備期間を測るために使用したり、信号同士で同期するためのタイミング合わせなんかに用いられているというわけです。

3.クロック信号の立ち上がり/立ち下がりが歪んだ場合の影響CLK/BCLK)

さて、クロック信号の役割がわかったところで、本題に入ります。

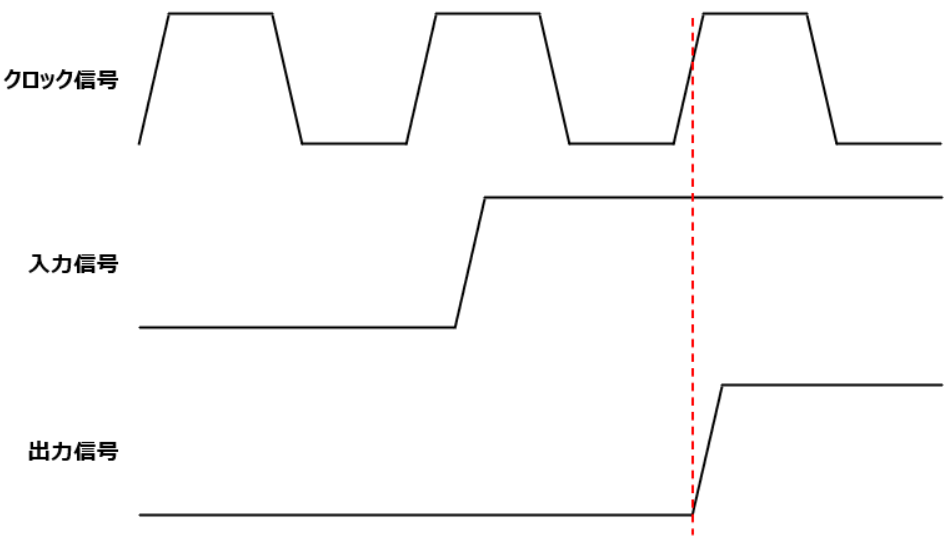

今、入力信号がHighに遷移し且つクロック信号の立ち上がりエッジを検出することで出力信号がHighになる機構を組んでいたとします。

以下のようなタイミングチャートになります。

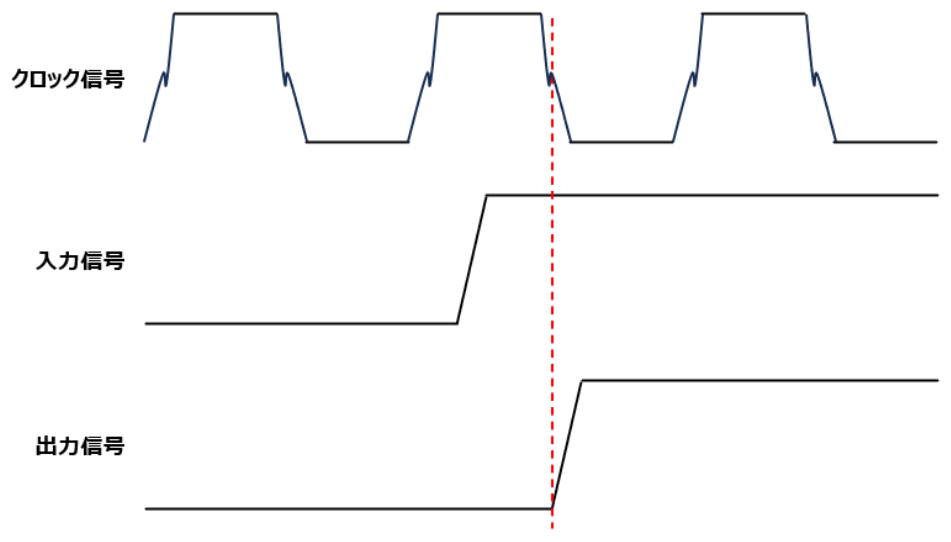

なのですが、もしクロック信号が歪んでいた場合、以下のように不正なタイミングで信号が出力されてしまう可能性があります。

立ち下がりのタイミングで出力されてしまっていますね。

これは、立ち下がり時の歪みによって一瞬反転して上昇した部分を立ち上がりだと誤判定してしまったということです。

仮にクロック信号の立ち下がりエッジを検出するようにしていたとしても、同様の現象は発生し兼ねないです。

何故そんなことが起こるのかというと、クロック信号の歪みがしきい値付近の電圧を行き来してしまっているからです。

通常、ICにはHigh判定となるしきい値と、Low判定になるしきい値が設定されています。

3.3Vの電圧信号があったとして、使用するICの入力電圧が0V~0.8Vの時はLow、2.8~3.3Vの時はHighという判定になるといった具合にです。

ただ、このICだと0.8V~2.8Vの間がHigh/Lowどちらの判定になるのかわからないですよね?

図4の例の場合、このHigh/Lowの判定が切り替わる微妙な箇所でクロック波形が歪んでいた為、運悪く立ち上がりだと判定されてしまったというわけです。

このように、クロック信号は立ち上がり/立ち下がりエッジを検出する用途である為、波形の歪みについてはしっかりと対策をする必要があります。

ノイズの発生しやすい部品や信号ラインを近くに配置しないようにしたり、クロック信号パターンをGNDで挟んで保護したり、基板設計時には注意しましょうね。

ちなみに、シュミットトリガ対応のICなら多少は許容できますが、タイミングによってはアウトなので、クロック信号に関しては綺麗な立ち上がり/立ち下がりになるように心掛ける方が無難です。

過信して市場不具合なんて出たらたまったもんじゃないですから…。

以上、「クロック信号の立ち上がり/立ち下がりが歪んだ場合の影響と除去しなければならない理由」についての説明でした。