今回は、「CMOSロジック」についての説明です。

1.初めに

トランジスタやFETは様々なICに使用されていますが、その中でもよく使用されている回路構造として“CMOS”というものが存在します。

何となく聞き覚えがあるのではないでしょうか?

というのも、このCMOSという回路構造は結構な頻度で色んな半導体製品に使用されているんですよね。

なので、CMOSを見たことがあっても、その構造がCMOSだと気付いていない可能性があります。

今回は、そんなCMOSという回路構成のロジックについて、わかりやすくまとめていこうと思います。

2.CMOSとは?

CMOSとは、pチャネル型とnチャネル型のMOSFETを組み合わせて構成した[Complementary(補完的)]な論理回路のことです。

読み方はシーモスです。

“補完型MOS”や“相補型MOS”と記述されていることもあります。

補完的とは“不十分な部分を補って完全な状態にする”という意味です。

なので、MOSFETの組み合わせで構成した補完的な論理回路であるならCMOSと呼ぶ為、CMOSという決まった回路構成があったり、CMOSという種類のMOSFETが存在するわけではありません。

CMOS回路を搭載したICのことをCMOSと呼んでいたりするので、勘違いしやすいんですよね。

世の中には様々なICが存在しますが、中身を見てみると結構な確率でCMOSロジックになっています。

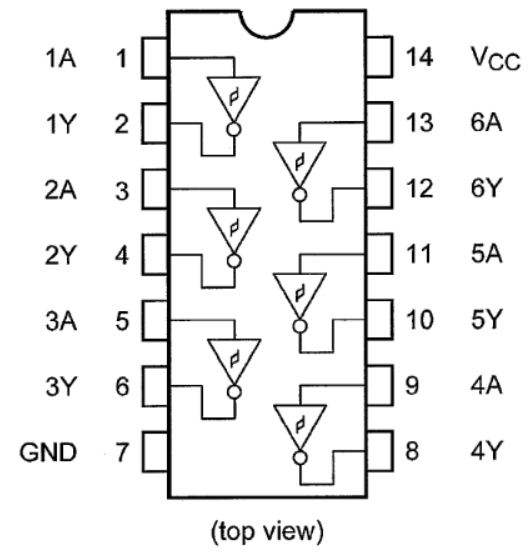

例えば、74VHC14FTという東芝製のICがあります。

このICの端子配置図は、以下のようになっています。

この図は、NOT回路が6つ内蔵されていることを指しています。

このICの名称は、“CMOSデジタル集積回路”です。

なので、このNOT回路はCMOSで形成しているのです。

ただし、データシートにもよりますが、MOSFETで構成した本当の回路構造まで載せていないことは多々あります。

だからこそ、CMOSとは何なのかが若干わかりづらくなっているんですよね。

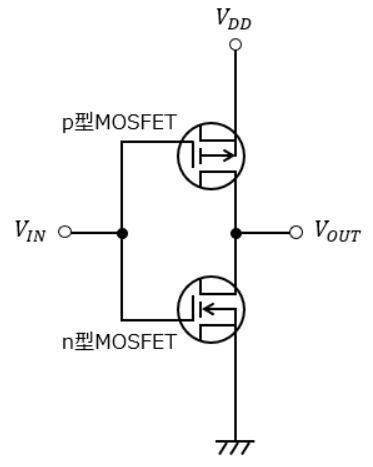

3.最も基本的なCMOS回路

CMOS回路は多々あるわけですが、その中でも最も基本的なCMOS回路は以下の通りです。

ロジックICの出力部によく使用されているので、データシート上の回路図にてよく見かけるのではないかと思います。

では、どんな回路なのか、動作について説明していきますね。

nチャネル型MOSFEETは、ゲート-ソース間電圧VGSがしきい値電圧VTを上回った時にONになります。

それに対してpチャネル型MOSFETは、ゲート-ソース間電圧VGSがしきい値電圧VTを下回った時にONになります。

前提条件として頭に置いておくべきなのはこの2点のみです。

要約すると、「図2の場合は入力信号がVDD(Highレベル)の時はnチャネル型MOSFETがONし、入力信号がGND(Lowレベル)の時はpチャネル型MOSFETがONする」です。

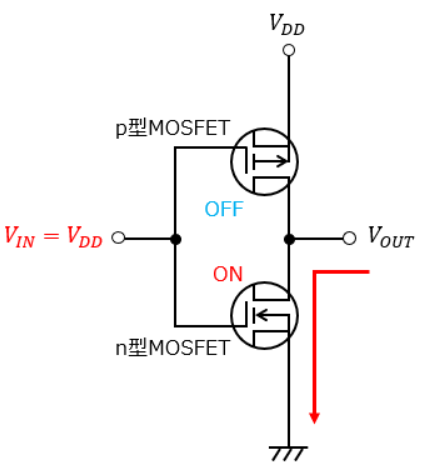

では、まずはVIN=VDDだった時について考えます。

VIN=VDDということは、入力信号がHighレベルの時だということです。

この入力信号が各MOSFETのゲート端子に入力されていますので、nチャネル型MOSFETだけONになります。

結果、以下のように回路が繋がります。

入力信号がHighレベルなのに対し、出力信号はGND/Lowレベルになるわけです。

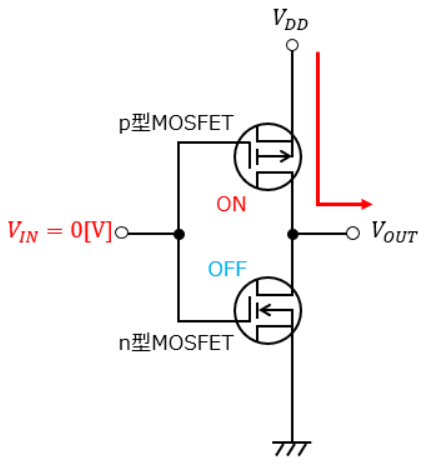

今度は、VIN=0[V]だった時について考えます。

VIN=0[V]ということは、入力信号がLowレベルの時だということです。

この入力信号が各MOSFETのゲート端子に入力されていますので、pチャネル型MOSFETだけONになります。

結果、以下のように回路が繋がります。

入力信号がLowレベルなのに対し、出力信号はVDD/Highレベルになるわけです。

つまり、このCMOS回路のロジックは、入力信号を反転させて出力するNOT回路(インバータ)になっていることがわかります。

このCMOS回路が最初に例に挙げた東芝製CMOSデジタル集積回路である74VHC14FTに内蔵されているのです。

4.実際のCMOS回路

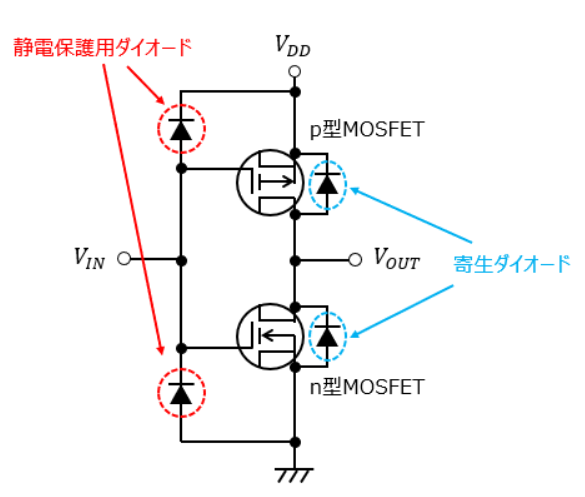

最も基本的なCMOS回路は図2の通りでしたが、実際には静電保護用のダイオード(※)が組み合わせてあることが多いです。

※外部端子から侵入してきたESDを吸収し、回路の誤動作を防止する用途で搭載するダイオードのこと。ここではMOSFETが誤動作をしないように保護している。

また、MOSFETのドレイン-ソース間には寄生ダイオードというものが存在し、出力端子側から意図していない電流が回り込んできたりした場合にうまく電流を逃がせるような構造になっています。

要するに、実際は以下のような回路になっています。

ただ、トレラント機能(駆動電圧以上の電圧を入力端子に印加できるようにした機能)を持った回路の場合、pチャネル型MOSFET側の静電保護用ダイオード及び寄生ダイオードは寧ろ誤動作を引き起こすようになってしまうので、敢えて搭載されていなかったりします。

この辺りは、別途トレラントの記事をまとめて説明すると予定です。

(※記事は出来ているけど編集優先度が後回しになっている。)

5.CMOSの特徴

CMOS回路は、以下のような特徴を持ちます。

図2の最も基本的なCMOS回路の動作を見てわかる通り、CMOS構造だとその時々で必要な部分のMOSFETのみスイッチング動作することになります。

図2の場合、p/nチャネル型MOSFETが動作している時はn/pチャネル型MOSFETが必ず休んだ状態になります。

スイッチングしてON状態にならない限り電流は流れないので、無駄な動作をしないように回路を休ませることが可能で、省電力ということになります。

MOSFETの消費電力自体は小さなものですが、LSIのような規模が大きなICだと内部に使用されているMOSFETの数が非常に大きくなります。

その為、熱暴走をして誤動作の原因になり兼ねないので、少しでも省電力であることはICとしては願ったりな性能だと言えます。

MOSFETを使用しているので、当然ながら高速スイッチング動作が可能です。

トランジスタを使用している恩恵ですね。

①の利点と被ってきますが、省電力であまり発熱をしないということは、それだけ部品を密集させて集積することが可能です。

その為、SoC(一つの半導体チップにある装置の動作に必要なシステムを実装する方式のこと)に向いています。

6.その他のCMOSロジック

最も基本的なCMOSロジックがNOT回路になっていましたが、他にも代表的なCMOSロジックは存在します。

それは、NAND回路とNOR回路です。

どんな回路構造になっているのかは別途まとめてあるので、以下の記事を参考にしてください。

以上、「CMOSロジック」についての説明でした。